DigilentのPYNQボードを使ってHDMIの入出力に関するプログラムを

ぼちぼち書いていたのですが, このボードではHDMIの入力が1系統しかないのと

メモリの帯域幅が足りないという問題に直面していました.

そこで自分好みのFPGAボードを作ろうということではじめました.

方針

必要な項目として以下の2点が上げられます.

- HDMIの入出力ポートが多く付けられる

- メモリの帯域幅とバンクを増やす

使用するFPGAはPYNQを踏襲しZYNQシリーズでXC7Z020です.

調べたところJLCPCBで6層基板を比較的安価で製造できそうなのと

6層基板ならBGA484ピンでもなんとかなりそうなので

XC7Z020-CLG48を使うことにしました.

メモリの帯域幅とバンクを増やすにはPS側のメモリだけでなくPL側にも

メモリを載せてしまうのが手っ取り早い解決策なのでPS及びPLにメモリが載ります.

また利便性を高めるためにFPGAボード自体に直接コネクタ類をつけるのではなく

ボードtoボードのコネクタを付けて別途拡張ボードを作ることで

拡張性をあげようと思います.

設計

設計するに当たりこのサイト(ACRi)を参考にさせてもらいました.

タイミングよく公開されていてとても役立ちました.

また, DigilentのFPGAボード PYNQやArtyも参考にしています.

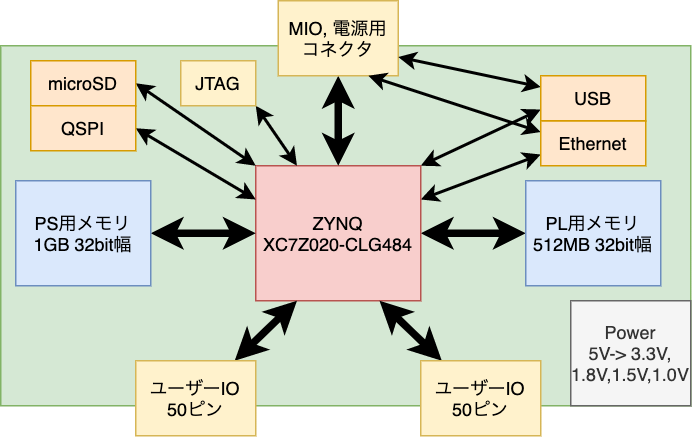

ブロックデザインはこの通りです.

PS側(ZYNQ側)

ZYNQに付随するメモリはせっかくなので1GBを搭載し,

microSDやQSPIもこのボードに載せます.

USBやEthernetも拡張ボード側で載せるとなるとSMD部品の実装が面倒だと

考えたのでこのボード側で必要な変換を済ませてしまいます.

この辺の配置は基本ピン配置が決まっているので

ただただICの仕様を比較し, 接続するだけの作業です.

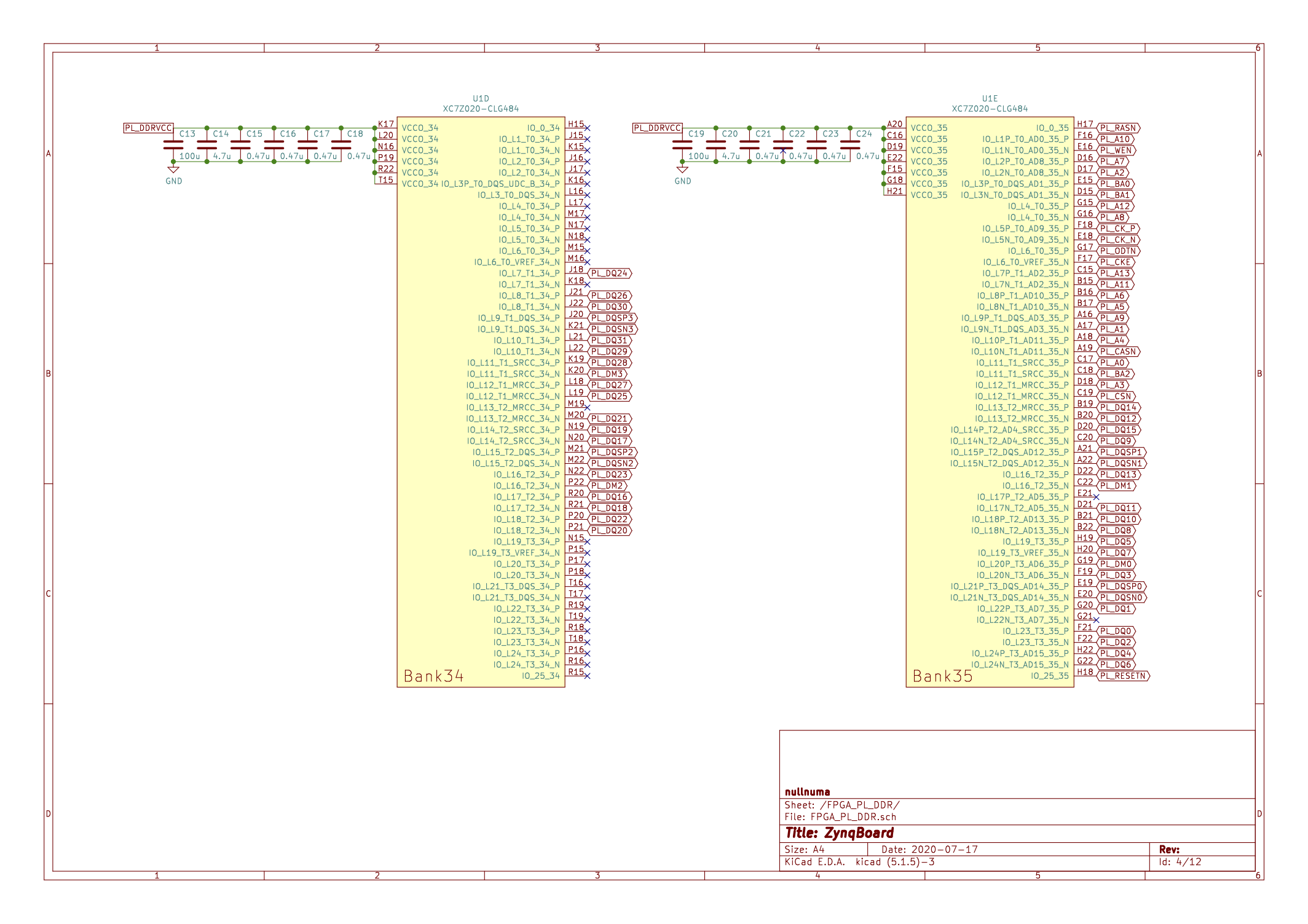

PL側

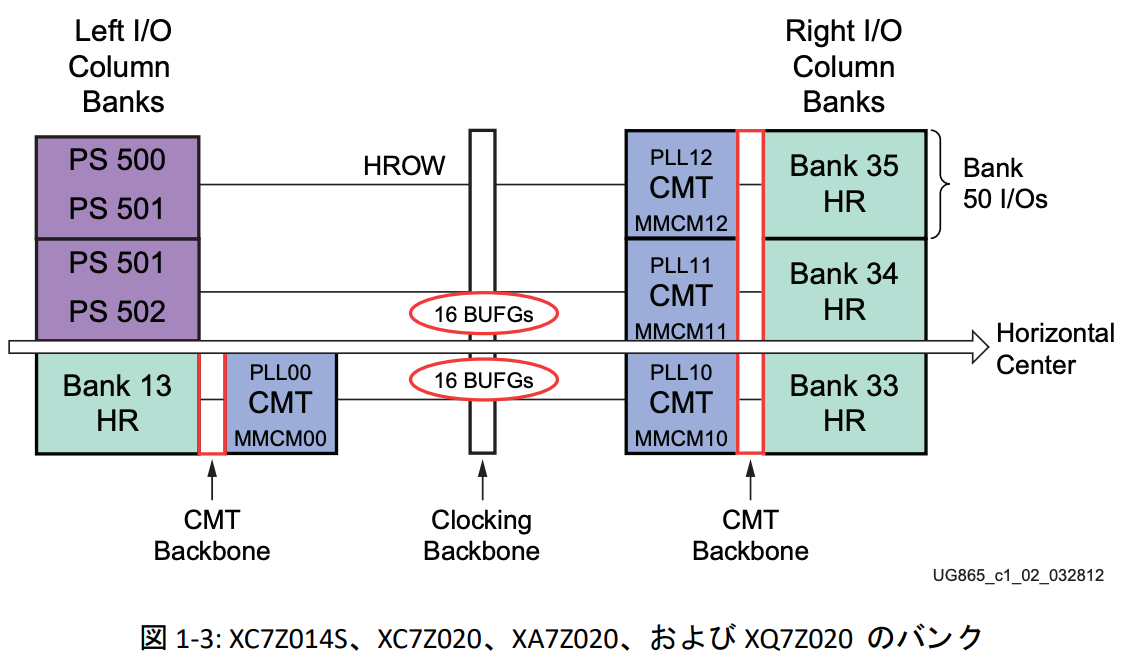

このFPGAにはバンクが13,33,34,35の4種類があります.

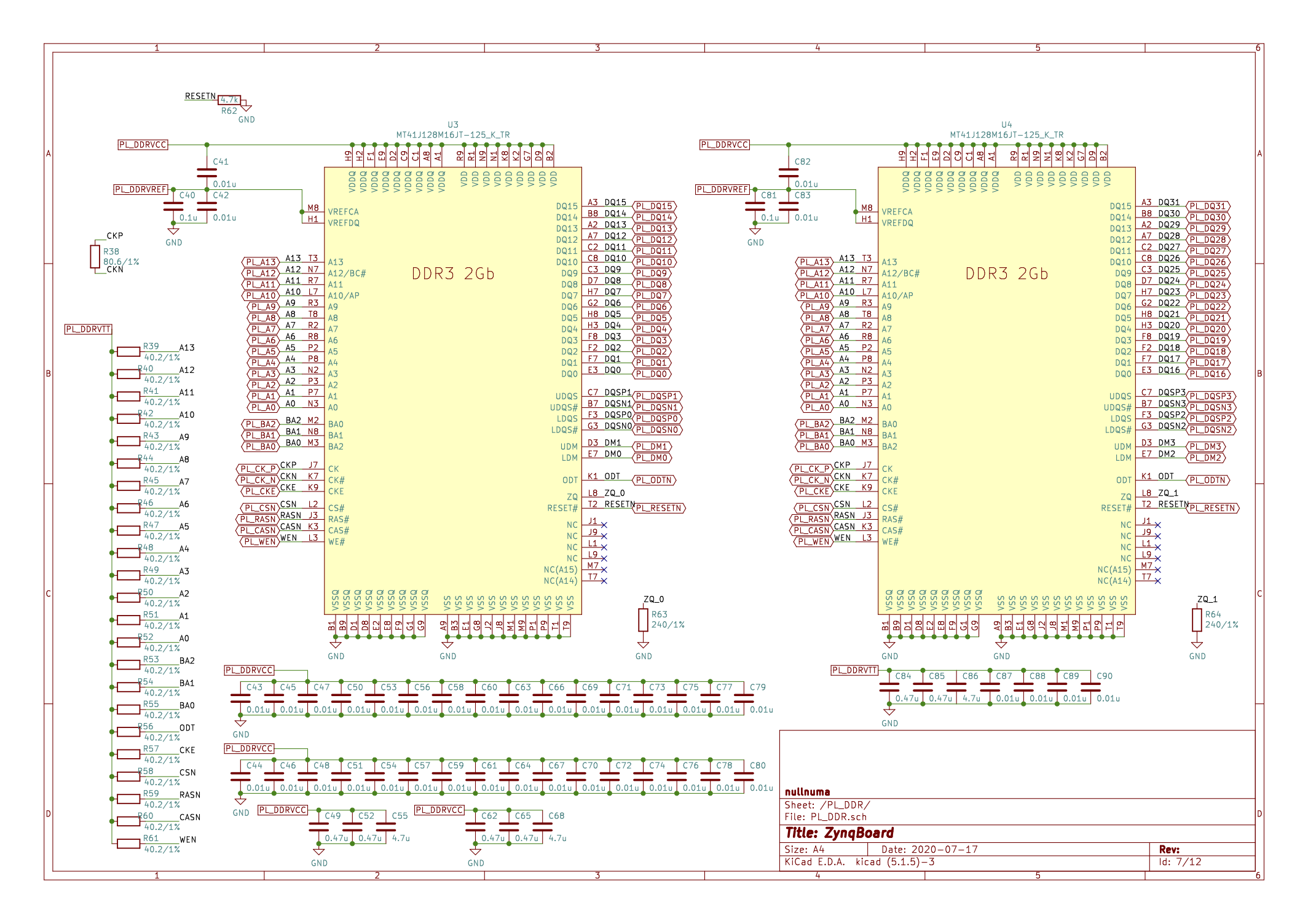

まずメモリについてですが

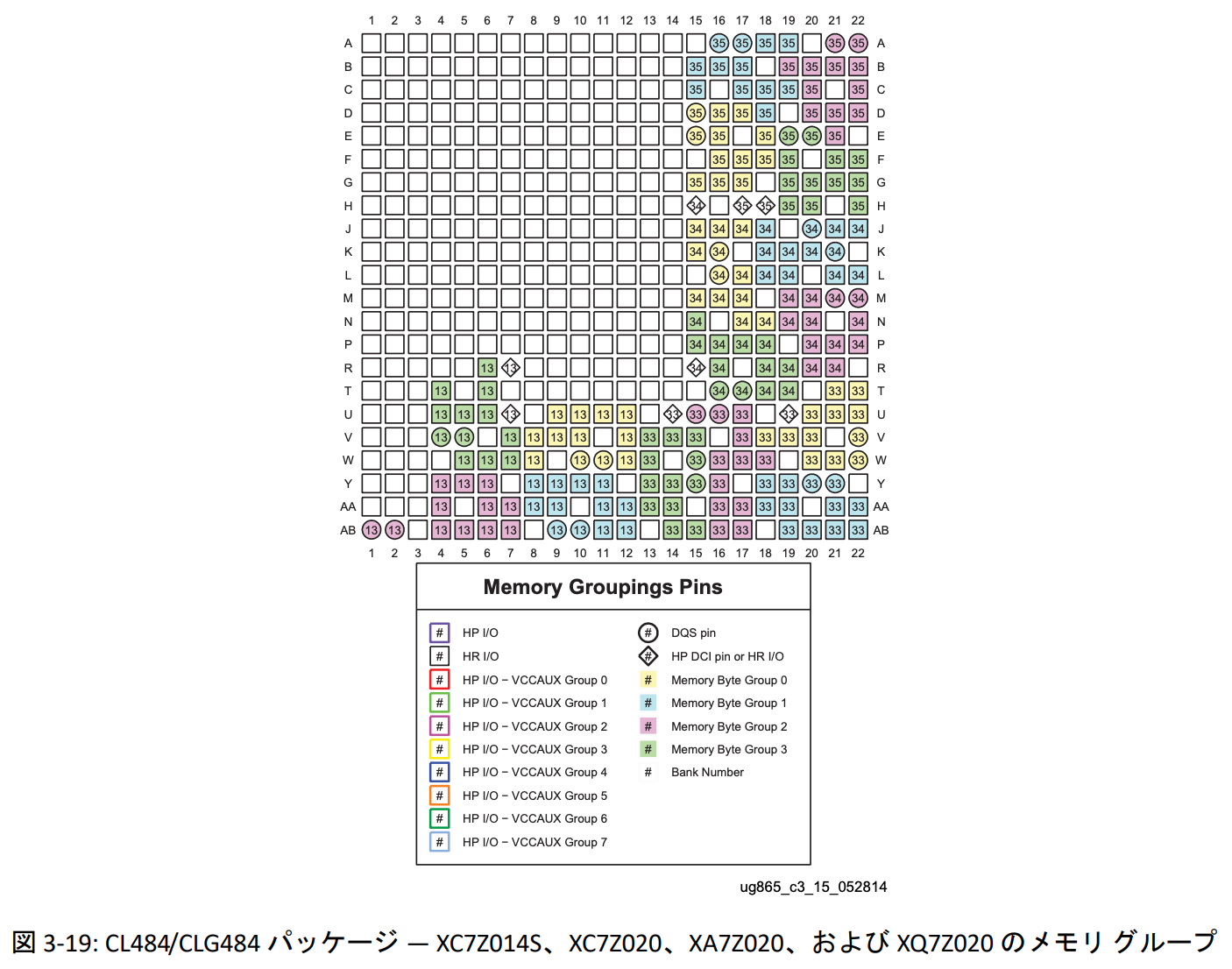

32bit幅でメモリを搭載するとなるとバンクは2個消費し, かつ垂直に隣り合ったバンクしか

使用することができない制限があるため, 以下の図よりバンク34,35を使用します.

(https://japan.xilinx.com/support/documentation/user_guides/j_ug865-Zynq-7000-Pkg-Pinout.pdf)

バンク内にも更に4分割されていてアドレス用として2グループ,

データ用はデータ0-7, データ8-15, データ16-23, データ24-31とわけて4ブロック使用します.

(https://japan.xilinx.com/support/documentation/user_guides/j_ug865-Zynq-7000-Pkg-Pinout.pdf)

クロック等のピンアサインには制限があるもののほかは

ほぼすべて好きなように配置できる(FPGAのいいところ!)ので

実際に基板を描いているときに随時入れ替えました.

配置するたびに問題ないピンアサインかVivadoのMIGジェネレーターで

確認を取りつつ設計しています.

ユーザIOについてはバンク13,33をそのままコネクタへ接続する形にしました.

100ピンあればいい感じに使えるでしょう.

まとめ

回路図の作成については既にあるFPGAボードを参考に作り上げることができました.

ピンの役割さえわかれば設計は単純な反復作業が多いことがわかりました.

もっと効率よくできればいいんですが…

特にメモリについては情報があまりなかったのでVivadoのピン配置で問題ないかを

確認していたのですがエラーならエラーとしか出さないので

どの配置がエラー吐いてるのかよくわからなかったのが辛いです.

次回は

この時点で実際に基板にすべて配線を終えることができるのかわからなかったのと

メモリ関連の配線のやる気がなさすぎて7月ぐらいに設計したのに

基板に起こす作業は10月下旬まで先延ばしにしていました…

いざ起こすとなると1週間かからずできましたのでそれについて次回書きます